| Sommaire: |

VIA C7 : Etude de l'Architecture

Aprés avoir vu les cartes en détail, il est maintenant temps de s'interesser au C7. Avant de rentrer dans les détails de son architecture, il est interessant de parler de son packaging et, pour être plus clair, de son physique (qu'on espère avantageux). L'occasion de vous annoncer que vous avons fait beaucoup de progrèss en photographie. Ne vous étonnez donc pas de trouver des très gros plans dans les articles à venir. Un petit aperçu :

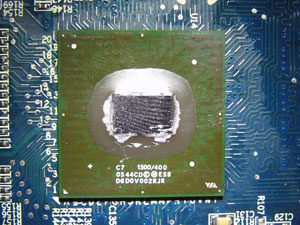

Mais revenons directement au C7. Ce processeur se présente sous la forme d'un composant BGA de 21 mm de côté. Bien plus petit qu'un C3 EBGA de VIA donc, qui mesurait 35 mm. Le C7 n'a pas d'IHS et donc, pas de protection du core, qui reste fragile. Un aperçu plus précis du processeur sur la carte mère :

Comme on le voit, ce processeur présente un die extrêmement petit, de seulement 30 mm² et ne consomme que 11 Watts à 1.5 GHz ! Voyons un rapide comparatif du C7 par rapport aux autres CPU :

Le record est clairement en faveur du C7 sur ce point. Celui-ci consomme d'ailleurs dix fois moins de courant qu'un Prescott et 60% de moins qu'un Pentium M classique. Reste a voir ce qu'il a dans le ventre, et, pour en connaitre plus, passons à l'étude en détail du core du C7.

- C7 : Architecture Interne

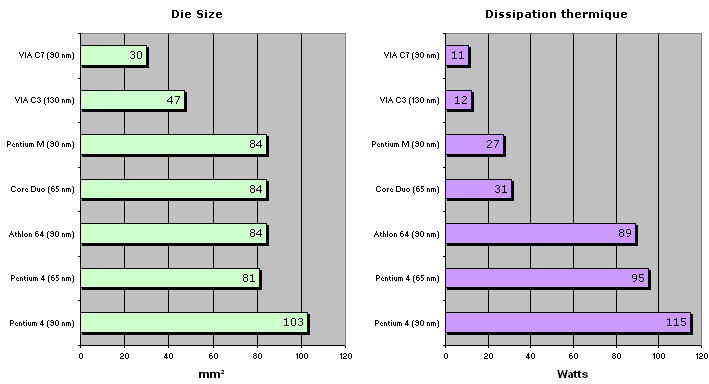

VIA fournit un schéma de block général de l'architecture du C7. Celui-ci va déjà nous permettre quelques remarques d'ordre général :

Le C7 est un processeur doté d'un pipeline à 16 étages. Comme le C3. Etrange coincidence ? La question est de savoir quelle est la taille du coeur d'exécution du C7 comparé au C3. Le calcul est assez simple :

- Le C3 comporte 20.4 Millions de transistors, un cache L1

de 2*64 Ko et un cache L2 de 64 Ko. Soit 192 Ko de cache. Un Mo de

cache SRAM-6T ECC classique correspond à 56.6 M de transistors.

Ces 192 Ko de cache "consomment" donc 10.6M de transistors. On peut en

déduire que la taille du core du C3 est de 20.4 - 10.6 = 9.8 M

de transistors

- Le C7 comporte 26.2 Millions de transistors, un cache L1 de 2*64 Ko et un cache L2 de 128 Ko. Soit 256 Ko de cache. Ces 256 Ko de cache "consomment" donc 14.2M de transistors. On peut en déduire que la taille du core du C3 est de 26.2 - 14.2 = 12 M de transistors

Le core du C7 est donc 20% plus gros que celui du C3. Cependant, il convient de noter que, sur ces deux millions de transistors d'écart, il faut retirer la gestion du bus QDR, la gestion du SSE3 et des options avancées de cryptographie. Et, au final, le core d'execution du C7 n'est pas beaucoup plus gros que celui du C3. C'est assez étonnant. Or, vu les performances très faible du C3, on s'attendrait à ce que VIA ait fait plus de modification sur le C7.

- C7 : Double PLL & Economie d'energie

Sur ce schéma, un composant attire l'oeil : Le PLL en bas, à droite. A quoi sert-il puisque nous avons pu voir clairement un PLL externe classique sur l'EPIA-EN ? A l'économie d'énergie. Etrange, mais c'est ainsi. En effet, VIA a fait particuliérement d'effort sur l'économie d'energie et le C7 consomme moins d'un watt en mode veille. Reste le probleme de la commutation. Si Intel a implémenté le SpeedStep sur le Pentium M, chaque transition de la fréquence d'horloge (à la hausse ou à la baisse), necessite environ 15000 cycles processeurs. Dans le cas d'un passage en mode économie d'energie, il faut d'abord diminuer la fréquence, puis, ensuite, réduire le voltage. Si ce dernier est réduit avant que l'horloge n'ait diminué, le processeur plante car il n'est plus suffisament alimenté pour la fréquence donnée.

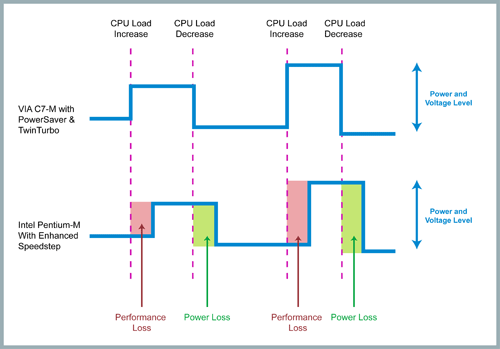

Or, VIA semble avoir trouvé une solution miracle pour régler ce probleme : Inclure deux PLLs a son processeur. L'un fonctionnant toujours à la fréquence maximum (celui de la carte mère) et un second, dans le processeur, qui fonctionne toujours à la fréquence minimale. Les changements d'états sont donc instantanés, comme on le voit sur ce schéma :

L'idée est séduisante sur le papier. Mais, pour être totalement efficace, il faut que les transistions soient les plus nombreuses possibles, ce qui suppose que le système d'exploitation l'indique correctement, immédiatement, et sans latence. Windows XP en étant bien incapable, il faudra se rabattre sur un driver, fourni par VIA, qui s'en chargera. De son efficacité dependra l'efficacité de cette astuce, baptisée TwinTurbo.

- C7 : Cryptographie et NX bit

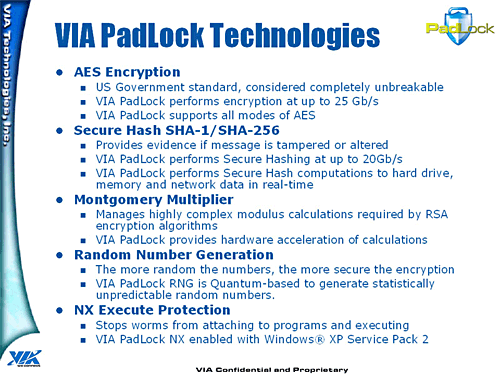

C'est un fait : Depuis le Nehemiah, VIA a marqué quelques points dans l'utilisation de ses techniques de cryptographies avancées nomées PadLock. En effet, pour tirer parti de ces fonctions hardware d'encodage/décodage, il faut que le logiciel soit reprogrammée pour en tenir compte. A l'heure actuelle, quasiment aucun developeur ne s'est lancé dans l'aventure. Et VIA doit se contenter de deux logiciels pour le moment. OpenSSH pour commencer, ce qui n'est pas le moins important des logiciels, et SunJCE, l'API de cryptographie intégrée dans JAVA. Le C7 apporte quelques nouveautés face au C3 :

Par rapport au C3, le C7 apporte principalement la gestion du RSA et du SHA. Deux algorythmes très utilisés dans les protocoles de sécurité sur Internet. Niveau résultats, inutile de se relancer encore une fois dans des benchmarks hasardeux dont la conclusion est déjà connue : Bien utilisées, les fonctions de cryptographies intégrées écrasent litterallement tous les autres processeurs en mode software, avec des calculs environ 50x plus rapide pour 1/3 de l'occupation CPU. Reste a convaincre les developeurs d'en tirer parti.

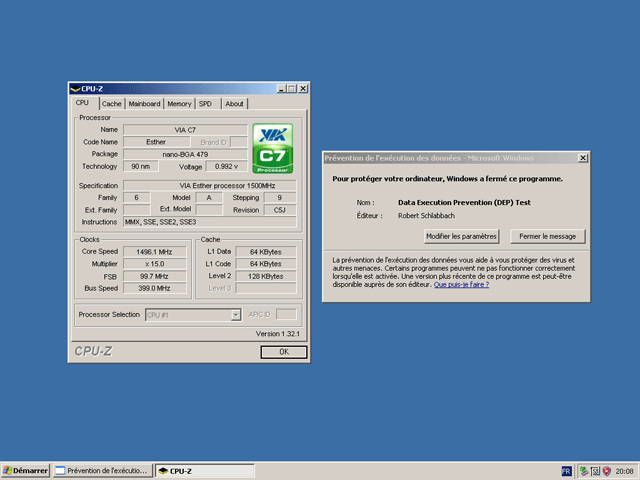

Parlons maintenant du NX Bit, inclus dans la quasi-totalité des processeurs modernes. Nous avons testé son bon fonctionnement sur une plateforme C7 sans problème :

Il est maintenant temps de s'intéresser au coeur d'execution du C7 en lui même.

- C7 : Coeur d'exécution

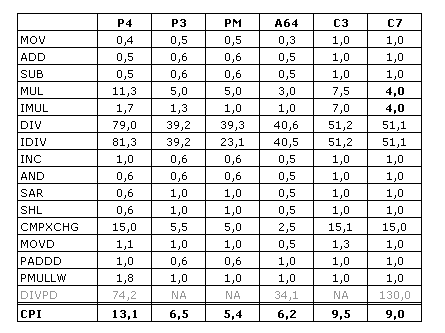

Comme nous l'avons dit, le C7 est composé d'un pipeline à 16 étages. La FPU fonctionne à 1x la vitesse du core, donc 1.5 GHz pour notre sample. Pour rappel, les anciens C3 été doté d'une FPU fonctionnant à la moitié de la vitesse du CPU, ce qui plombait encore plus les résultats. Nous avons cherché à connaître les modifications du coeur d'execution effectuée par VIA sur le C7. Pour ce faire, nous avons mesuré le nombre de cycle necessaires à l'execution d'instructions courantes et nous l'avons comparé aux autres plateformes. Voici les résultats :

C'est un fait : le core d'exécution du C7 est très proche de celui du C3. On note toutefois une nette amélioration des multiplications entières et flottantes qui passent de 7 cycles à 4 cycles. Si ce résultat est excellent en entier, il laisse à désirer en flottant. Mais ce type de calcul n'a jamais été le fort de VIA. Niveau SSE, le CPU patît visiblement des faibles performances de l'unité FPU. Avec 130 cycles pour un DIVPD (SSE2), il est quatre fois plus lent qu'un Athlon 64. Malgré tout, le C7 n'a jamais été dédié à des applications très gourmandes en ressources CPU.

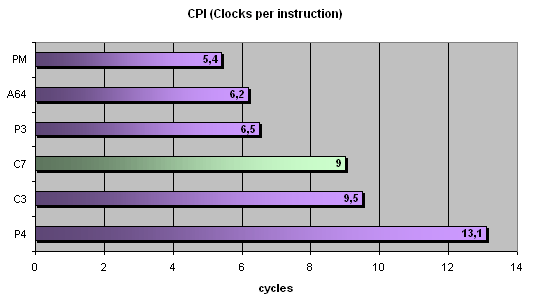

Nous avons également calculé un CPI (nombre de cycles moyens par instructions) sur ces processeurs. Les résultats sont intéressants :

Selon ce graphe, le coeur d'execution de l'Athlon 64 est deux fois plus performant à fréquence égale que le coeur d'exécution du Pentium 4. Nous ne sommes donc pas loin de la vérité. Le C7 se situe entre le P4 et l'A64 en terme d'efficacité. il est 5% plus performant que celui du C3, ce qui n'est pas exceptionnel. Ceci dit, le gain en fréquence devrait permettre un gain de performances appréciable. Mais il est maintenant tant de voir les performances du cache.

- C7 : Caches L1 & L2

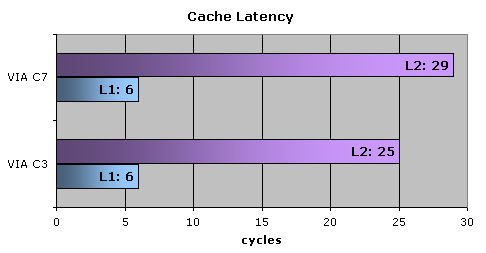

Parlons maintenant des caches du C7. On le sait, le C7 est constitué d'un cache de donnée L1 de 64 Ko et d'un cache d'instructions L1 de 64 Ko. Celui-ci est couplé avec un cache L2 de 128 Ko. Ce cache fonctionne en 32-way associative. Une première. Nous avons commencé par mesurer sa latence comparé au C3 :

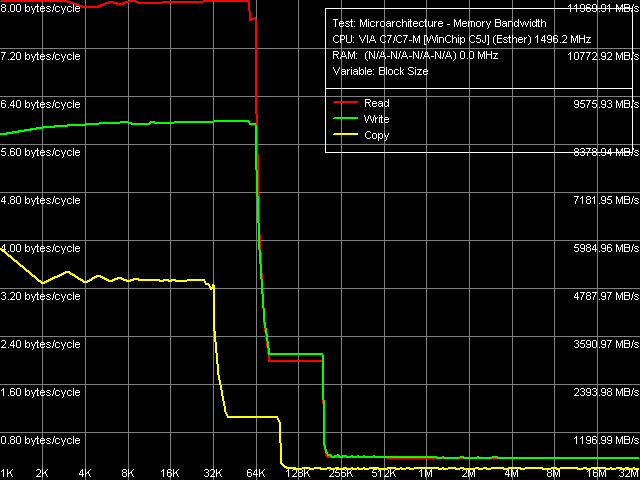

Si le L1 ne bouge pas, le L2 passe de 25 à 29 cycles. Cette modification a très probablement été effectuée pour tenir la montée en fréquence. Il est maintenant temps de voir le débit du cache et, pour cela, rien de vaut une passe de RMMA :

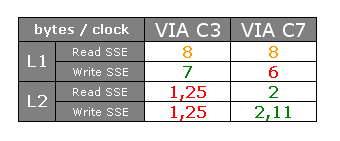

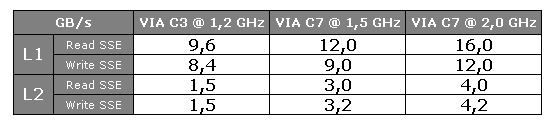

Ramené au C7, nous avons comparé les débits des deux caches :

Si le L1 en écriture souffre d'un débit un peu moins important, le L2 est 60% plus rapide ! Ramené aux fréquences nominales des processeurs, le gain est apréciable :

Le C7 à 1.5 GHz offre ainsi un cache L2 deux fois plus rapide que le C3 à 1.2 GHz. Un gain apréciable qui devrait se traduire dans la pratique par de meilleures performances.