Nehalem : Uncore (QPI & PCU)

Il est maintenant temps de s’intéresser à l’Uncore. Petit rappel : l’Uncore englobe tout ce qui a été intégré dans le microprocesseur mais qui ne constitue pas les Core en eux-mêmes. On trouve principalement dans l’Uncore le cache L3 et le contrôleur mémoire que nous avons déjà vu précédemment, mais aussi le nouveau bus QPI et le PCU (Power control Unit – Gestionnaire d’énergie) que nous allons voir maintenant. Mais avant cela, il est important de comprendre que les fonctionnalités de l’Uncore répondent d’abord à un besoin primordial : la modularité.

En effet, l’intégration du contrôleur mémoire, même s’il permet les gains très importants en latence et en bande passante que nous avons observé, à tout de même un gros désavantage par rapport aux Northbridge classique : le moindre changement sur la mémoire entraine un nouveau Socket et donc un remplacement de la carte mère. C’est pour cette raison que les sockets se sont multipliés chez AMD depuis la sortie de l’Athlon 64. Pour tenter de compenser ce problème, Intel a conçu Nehalem dans une optique de flexibilité, afin de pouvoir le décliner à l’envi sur tous les segments du marché, de l’entrée de gamme aux serveurs multiprocesseurs. C’est bien sûr le cas des Core en eux-mêmes, qui sont organisés en blocs afin de pouvoir en supprimer deux très facilement, mais aussi de l’Uncore. |

|

Le cache L3 est ainsi architecturé en blocs de 2 Mo pour pouvoir le tronquer rapidement sur les déclinaisons moins chères ; le nombre de canaux du contrôleur mémoire est ajustable (les prochains Core i7 ne disposeront d’ailleurs que de deux canaux), tout comme le nombre de liens QPI. Pour parfaire le tout, Intel a aussi prévu dès l’origine (mais reste nettement plus discret sur ce point) une interface pour connecter deux dies dans un même package, comme sur les Core 2 Quad, et proposera bientôt un processeur doté d’un IGP (cœur graphique intégré). Il sera donc simple et peu couteux pour le fondeur de proposer des Nehalem dotés de seulement deux cœurs et de 4 Mo de cache L3, ou bien des processeurs 2 * 4 cœurs embarquant 16 Mo de L3. Tout cela, selon les besoins du marché.

- Bus QPI (Quick Path Interconnect)

Autrefois connu sous le nom de code CSI (Common Systems Interconnect), le bus Quickpath a pour ambition de proposer une alternative à l’HyperTransport d’AMD. Il s’agit d’un bus d’interconnexion rapide chargé de relier deux processeurs ensembles (ou plus) et même de prendre en charge la liaison entre le CPU et le « Northbridge », réduit au rang de pont PCI Express. Soyons tout de suite clair : le bus QPI n’a d’intérêt que pour les systèmes multiprocesseurs et est donc principalement réservé aux serveurs. Les prochaines déclinaisons « grand public » des Core i7 (Lynnfield) ne comporteront d’ailleurs aucuns liens QPI et l’interconnexion avec les autres composants sera effectuée par le biais d’un contrôleur PCI Express classique.

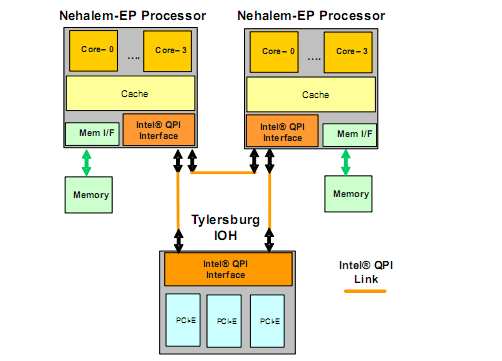

Les Bloomfield (Core i7) et Nehalem-EP (Xeon) disposent toutefois de deux liens QPI. Comme on le voit sur le schéma ci-dessus, l’un est chargé de la communication avec un autre CPU (et donc inutilisé sur Bloomfield, du moins jusqu'à ce qu’Intel ne sorte sa nouvelle plateforme Skulltrail) et l’autre est connecté au chipset Tylersburg, dorénavant connu sous le nom « Intel X58 ». Techniquement, le bus QPI est un bus sériel constitué de 2*20 lignes (20 lignes pour l’émission, 20 lignes pour la réception) par lien QPI. Chaque lien est capable d’effectuer 6.4 milliards de transferts par secondes (GT/s), ce qui correspond à un débit 12.8 Go/s de manière bidirectionnelle, soit un total de 25.6 Go/s pour un lien complet. Intel prévoit aussi dans ses spécifications le fonctionnement du bus PCI à 5.83 GT/s (23.3 Go/s) et même à 4.8 GT/s (19.2 Go/s). Dans le futur, ce chiffre devrait rapidement grimper jusqu’à 8 GT/s afin de parvenir aux 32 Go/s déjà atteint par le bus HT des derniers Opteron.

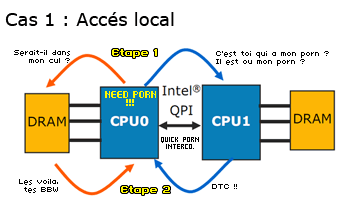

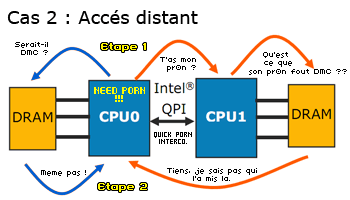

En restant dans le domaine des plateformes multiprocesseurs, qui dit contrôleur mémoire intégré et bus d’interconnexion rapide dit NUMA, ou « Non-Uniform Memory Access ». Car en effet, auparavant, tous les CPU d’un environnement multi-cœur accédaient à la mémoire par le biais d’un Northbridge qui faisait office de contrôleur mémoire unique. Maintenant que chaque CPU disque de sa propre mémoire, il fallait prévoir un dispositif permettant, pour un CPU, d’accéder à la mémoire d’un autre CPU. Bien sûr, l’accès à une donnée située dans de la mémoire gérée par un autre CPU entraine forcement une latence plus importante et un débit limité par le bus d’interconnexion. Plus ce dernier sera rapide, plus les performances du sous-système mémoire dans un environnement SMP seront bonnes.

|

|

Dans le cas d’un accès distant, la faible latence et le débit important du lien QPI permettra donc d’effectuer des transferts de grosses quantités de données rapidement entre les CPU. Ceci est encore plus critique dans le cas d’une plateforme dotée de quatre CPU puisque la mémoire disponible sera alors divisée en quatre, de quoi faire exploser l’utilisation du bus QPI.

- PCU (Power Control Unit)

Intel a fortement amélioré les capacités d’économie d’énergie de Nehalem pour des raisons techniques, un peu, mais surtout pour des raisons marketing. Car après avoir promis qu’on ne l’y reprendrait plus avec les problèmes de dissipation thermique excessive des Pentium 4 et que l’objectif était de limiter le TDP à 65 Watts sur les processeurs grand public, force est de constater que les premiers Core i7 sont dotés d’une enveloppe thermique de 130 Watts.

Pour tenter de limiter le problème, Intel parie sur la consommation électrique moyenne et non plus maximale. Le but étant que chaque petite partie du CPU soit immédiatement mise en veille en cas d’inactivité et cela, même pour quelques millisecondes. Pour gérer tout cela, l’Uncore de Nehalem comprend un nouveau composant très important : le PCU. Celui-ci est un microcontrôleur évolué, chargé de gérer en temps réel toutes les multiples fréquences générées au sein du CPU ainsi que les tensions d’alimentations. Il s’agit en fait d’un cerbère très performant qui régule extrêmement rapidement les fréquences et tensions des Cores et de l’Uncore en fonction de variable (température, courant consommé, …etc.), mais aussi de constante. Intel peut ainsi définir un TDP maximum que le PCU se chargera de respecter et ce, quelques soit la fréquence et la tension appliquée au CPU par la carte mère !

|

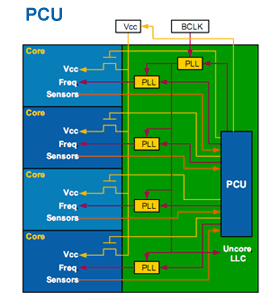

Sur Nehalem, le PCU gère tout, voit tout, contrôle tout, et ce, en lieu et place de la carte mère. La fréquence fournie par la carte mère (Base Clock – BCLK) n’est ainsi plus transmisse directement aux Core ni même à l’Uncore puisqu’elle est régénérée par un PLL interne piloté par le PCU. Ainsi, la carte mère peut toujours envoyer 166 MHz au lieu des 133 MHz nominaux, cette fréquence pourra parfaitement être corrigée par le PLL interne et repositionnée à 133 MHz. Le PCU contrôle ainsi un PLL par cœur et un autre pour l’Uncore, auquel il applique des ratios. La fréquence finale est obtenue par la fréquence de base (BCLK), multipliée (ou divisée) par le ratio du PLL concerné. Il est donc impossible de « forcer » une fréquence sur l’un des cœurs. Les overclockers en seront pour leurs frais si Intel décide de brider le tout.

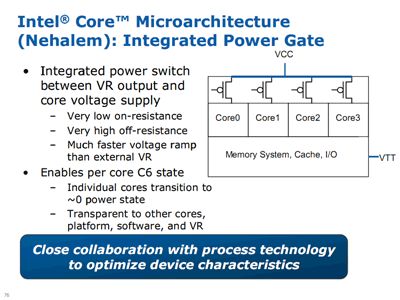

Mais le pouvoir du PCU ne s’arrête pas là. En effet, celui-ci est aussi en charge des tensions d’alimentations des différentes parties du CPU et, de la même manière que les signaux d’horloge sont reconditionnés, le courant est lui aussi régulé par le biais de MOSFET de puissance directement intégré au die ! Le PCU peut ainsi contrôler exactement la tension qui alimente chaque cœur de manière nettement plus rapide et beaucoup plus fine que les régulateurs de la carte-mère. Cette fois, ce sont les fabricants de carte-mères qui en seront pour leurs frais car leurs technologiques d’économie d’énergie à ce niveau perdent quasiment tout de leur intérêt.

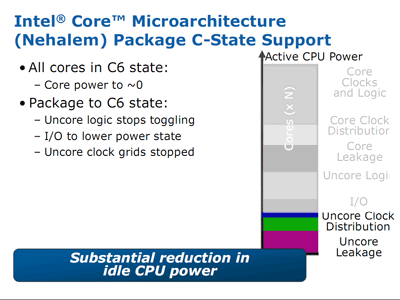

Tout ceci permet à Intel de proposer un mode d’économie d’énergie C6 amélioré. Car grâce à la régulation interne des horloges et des tensions, il devient possible de totalement interrompre l’alimentation électrique d’un cœur (et non plus de seulement réduire la tension) de manière indépendante des autres ! Ceci élimine par la même occasion les dernières sources de pertes : le leakage au niveau des transistors même. Selon Intel, l’extinction complète et indépendante des cœurs en mode C6 devrait permettre une réduction d’environ 20% de la consommation électrique (et de la dissipation thermique) lors d’une utilisation classique (comprenez : non intensive) du Core i7 par rapport au Core 2.

Il ne restera plus d’alimenté sur un processeur très faiblement utilisé (dont tous les cœurs serait en mode C6) qu’une faible partie de entrées/sorties et le système de distribution des horloges de l’Uncore, plus le leakage associé aux deux. Vu que l’Uncore représente 20% du total de consommation électrique d’un Core i7, on peut estimer que la puissance requise dans ce cas tombera à environ 12-13 Watts, ce qui reste très remarquable. Nous en saurons plus dans l’étude de la consommation à la fin de cet article.