Après l'annonce par VIA du nom commercial (C7) du nouveau core C5J, nous avons pu obtenir plus d'informations sur le successeur du C3. Le futur CPU Esther (nom de code du C5J/C7), est actuellement prévu pour le début de l'année 2005 et adoptera les technologies qui font cruellement défaut à l'actuel C3, dont nous avons démontré les carences dans un article récent. Bref, voyons plus en détails un des slides de présentations :

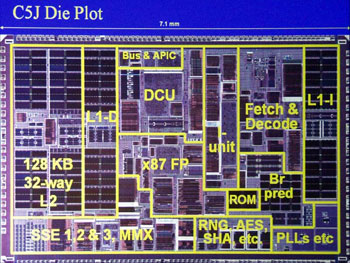

Première information, le CPU a dore et déjà été "Taped Out", c'est à dire que les premiers samples ont été produits. On sait également qu'il sera produit par IBM avec leur technologie 90nm SOI low-K, très proche de celle utilisée par les Athlon 64 90nm. Il utilisera ensuite un bus externe compatible Banias et donc, compatible P4. Le FSB sera de 200 MHz et le CPU supportera les architectures SMP 2-way et 4-way. Au niveau du core, le C7 inclura les instructions MMX, SSE, SSE2 et SSE3 ainsi que les fonctionnalités de sécurité via des unités dédiées à l'encodage. Niveau cache, le C7 embarquera 128 Ko de mémoire cache L1 en 4-way et 128 Ko de mémoire cache L2 en 32-way ! Certes, l'associativité des caches est très étrange...

Niveau spécifications, le C7 est prévu pour une introduction à 2.0 GHz, avec une dissipation thermique d'environ 15 Watts à 2 GHz et 3.5W à 1 GHz. Niveau performance, VIA espère péniblement obtenir les performances d'un Celeron 1.2 GHz avec un C7 2 GHz. Ceci serait toutefois suffisant pour de nombreuses applications. Un mot sur le die, le C7 sera doté d'un minuscule die de 31.7 mm² embarquant 26.2 Millions de transistors, ce qui est peu. Voyons d'ailleurs ce die plus en détail :