| Sommaire: |

![]()

Présentation du Chipset [SiS655TX]

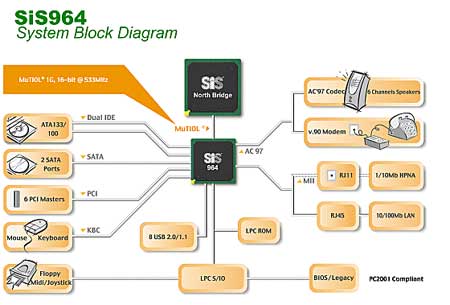

Enfin du nouveau dans le domaine des chipsets ! Depuis l'i875P d'Intel annoncé en début d'année, nous avons finalement eu peu de choses à se mettre sous la dent. Côté VIA, nous attendons toujours le PT880 moult fois retardés alors que côté SiS, le premier SiS655 n'a pas vraiment convaincu. Voulant revenir sur le devant la scène une nouvelle fois, SiS a donc récemment sorti le SiS655FX, immédiatement remplacé par le SiS655TX. Compatibles pin-à-pin, ces deux chipsets sont identiques, à l'exception d'une technique d'optimisation de la mémoire implémentée dans la révision "TX" par SiS. Côté architecture, le couple SiS655TX / SiS964 qui forme le chipset SiS655TX est basé sur l'AHSE. Sous cet acronyme barbare se trouve en fait le "Advanced HyperStreaming Engine". Un ensemble de technologie très technique visant à améliorer les différents goulets d'étranglement et donc à maximiser la bande passante disponible et minimiser la latence. Nous allons étudier tout ceci en commençant par la partie Northbridge pour nous intéresser ensuite au Southbridge. Commençons par voir un schéma global de ce chipset :

Comme on le voit, il s'agit d'une nouvelle génération de chipset qui n'a plus grand chose à voir avec le premier SiS655, sorti il y a maintenant un an. La gamme FX est basée sur une technologie que SiS appèle "HyperStreaming". Nous ne rentrerons pas ici dans les détails de cette architecture qui mériterait à elle seule un article complet. Pour faire simple, il s'agit en fait d'une optimisation des flux entre les différents composants de la machine. Il existe quatre type d'optimisations dans l'HyperStreaming, certaines visant à diminuer la latence via un système de priorité des flux, d'autres à augmenter le débit par un fonctionnement "en pipeline" du bus de communication. Pour plus d'informations sur cette technique, SiS propose une animation flash très bien faite (voir ici). Pour notre tour d'horizon, commençons par détailler le southbridge SiS655TX.

- NorthBridge SiS655

- Bus Processeur et AGP

Côté bus processeur, pas de réélle nouveauté ici. Le SiS655TX supporte sans problème toute la gamme de processeurs Intel, du Willamette jusqu'au prochain Prescott qui sera disponible d'ici quelques mois. Le SiS655TX peut donc gèrer toutes les fréquences de FSB possible, de 100 Mhz (400QDR) à 200 Mhz (800QDR) ainsi que toute la gamme de Celerons produite jusqu'a aujourd'hui. Bien sur, SiS s'est aussi mis à la page concernant l'HyperThreading et cette technologie est supportée sans probleme. Côté AGP, nous avons ici droit à un controleur AGP 8x standard qui supporte également l'AGP 4x et le Fast Write. Petite nouveauté, SiS a intégré la mise à niveau 3.5 des spécifications de registres AGP. Ceci dit, rien de bien palpitant sur ces deux bus et nous pouvons maintenant passé à beaucoup plus interessant

- Contrôleur Mémoire

La base du controleur mémoire inclut dans le SiS655TX est basée sur celle qu'on pouvait trouver dans le SiS655. Heureusement, SiS l'a grandement stabilisé et amélioré en terme de performances. Toujours capable de supporter la DDR400 ainsi que la DDR333 et la DDR266, il est de type Dual channel et peut donc gèrer simultanemment deux canaux afin d'accroitre les performances. Bien qu'il ne supporte ni l'ECC ni les mémoires de type "Registered", le SiS655TX accepte jusqu'a un maximum de 4 Go de mémoire. Autre point à signaler, la présence d'une multitude de coefficients mémoire permettant de désynchroniser le bus du processeur du bus mémoire. On pourra ainsi faire fonctionner de la DDR333 avec un P4 'C' comme l'i865 ou de la DDR500 avec un bus à 200 Mhz. Le Northbridge est donc composé de deux controleurs mémoires comme on peut le voir ci dessous :

Particularité très intéressante des chipsets Dual Channel SiS, la possibilité de fonctionner en mode "2x64 bits" en plus des classiques modes "1x128 bits" et "1x64 bits" de tous les chipsets Dual DDR actuels (i865, i875, nForce ..etc.). Pour simplifier, le mode 2x64 bits offre un gain de performance au cas ou l'utilisateur utilise deux modules mémoires de capacité différentes. Sans parvenir aux gains obtenus en 1x128 bits (modules identiques), le mode 2x64 bits est tout de même très intéressants. Voyons les différentes combinaisons possibles face aux i865/875 d'Intel :

Combinaisons possibles

du SiS655TX face aux i865/i875

En termes de performances, on obtiendra :

Mode 64 bits classique

< Mode Dual 64 bits < Mode 128 bits |

Bien que tout nouvel acheteur achetera soit un seul module de mémoire, soit deux identiques, la possibilité du mode Dual 64 bits peut être interessante en cas d'upgrade, ce qui n'est pas déjà pas si mal. Bien que nous verrons d'ici quelques pages les performances du SiS655TX, revenons un peu sur les différences qui ont poussé SiS a remplacer le 655FX par le 655TX. La seule différente entre les deux, c'est le PAT ! Certes, la version de SiS du PAT ne s'appele de la même facon que celle d'Intel, mais technologiquement, nous sommes ici dans le même cas. Plus complexe, l'implémentation de SiS est plus complexe à comprendre. Elle se divise en fait en trois étapes. Voyons ca :

I) Etape 1 : Valable dans tous les casContrairement aux autres, la première amélioration de SiS est valable quelque soit le mode de fonctionnement du chipset. Il s'agit ici de réduire la latence lors du passage des données dans le Northbridge. Un northbridge est constitué de deux PHY. Un PHY ou "Physical Layer Interface" est une interface permettant d'adapter les signaux entre l'extérieur et l'intérieur du composant. Les tensions et l'amplitude des signaux utilisées à l'intérieur du Northbridge par les circuits logiques est par exemple différente de celle requise pour la communication CPU <-> Northbridge. le rôle du PHY est d'adapter ces tensions. Dans le cas d'un chipset comme le SiS655TX, il y a plusieurs PHY, chaque passage dans un de ces PHY entraîne une latence de 1T. Pour réduire cette latence, SiS a virtuellement fusionné le PHY qui fait l'interface CPU <-> Northbridge avec celui qui s'occupe de l'interface Northbridge <-> RAM, ce qui permet d'économiser 1T a chaque passage, dont 2T au total. Un petit schéma valant mieux qu'un long discourt :

II) Etape 2 : Valable uniquement en mode 128 bits

Cette fois, l'optimisation n'est valable qu'en mode Dual Channel complet, c'est à dire en mode 128 bits. Il s'agit en fait de bypasser une étape, baptisée RDQ dans le processus de retour des informations. Autant vous l'avouer tout de suite, nous n'avons pas pu trouver d'explications sur ce "RDQ". Voyons le schéma et tentons une explication :

Ceci est une pure extrapolation, mais RDQ pourrait bien signifier "Random Data Queue", c'est à dire une sorte de petit buffer ou les données issues des deux contrôleurs mémoires sont remises en ordre et dans le bon sens pour être renvoyée au CPU. Dans ce cas, ce "RDQ" n'aurait pas lieu d'être en mode 1x128 bit ou 1x64 bits puisque les informations reviennent dans l'ordre dans ces modes et pourrait être bypasssé. Si c'est bien le cas, ce RDQ est plus inhérent au mode 2x64 bits qu'aux autres et ne constituent pas une réelle innovation, mais uniquement une fonctionnalité permettant le mode 2x64 bits sans pertes de performance dans les autres modes qui n'ont pas besoin de cette étape.

III) Etape 3 : Valable uniquement en mode synchrone

Cette fois, l'optimisation n'est valable qu'en mode synchrone, c'est à dire en DDR400 avec un Pentium 4 'C' ou en DDR266 avec un Pentium 4 'B'. Cette fois, c'est la ligne ADS (Adress Strobe), ligne de sélection d'adresses mémoires, qui est visée. De nouveau, il s'agit de bypasser une bascule (flip-flop) dans la logique interne du chipset. Voyons ça :

Sans savoir exactement de quoi il s'agit, il y a toutefois fort à parier que cette bascule ait un rapport avec la gestion du coefficient multiplicateur. En effet, le bypass ne peut fonctionner qu'en mode 1:1 et pas autrement. Probablement une étape de décomposition des données utile uniquement en mode désynchronisé.

Voila donc pour les améliorations apportées au "PAT", façon SiS. Nous verrons dans la pratique l'effet de ces ajouts techniques. Quoi qu'il en soit, ceux-ci doivent être tout de même conséquent vu la quasi annulation du SiS655FX.

- MuTIOL (Multi-Threaded I/O Link) 1 Go/s

De la même façon que le V-Link de Via ou le Hub-Link d'Intel, le bus MuTIOL a pour principal intérêt de laisser respirer le bus PCI lors des échanges entre les deux composants (Northbridge et Southbridge). Les SiS645 et 645dx communiquaient via un bus de données 16 bits Bi-Directionnel cadencé à 266 Mhz, ce qui leurs permettaient d'obtenir 533 Mo/s de bande passante maximale théorique. Pour les 648 et toute la gamme 655, SiS à boosté son MuTIOL en proposant un bus cadencé à 533 Mhz, ce qui lui permet une bande passante maximale théorique de 1.066 Go/s. Vu l'intégration de l'USB 2.0, du SATA et du FireWire, grands consommateurs de ressources, on ne peut que saluer cette initiative. Voici un petit comparatif des performances qu'offre les différents bus de communications Northbridge/Southbridge.

On retrouve le V-Link dans les premiers chipsets VIA (P4X266, P4X266A, ...etc), le V-Link 2 dans les chipsets plus recents (P4X400, PT800, ...etc), le Hub-Link chez Intel (i845E, i845G, i850E, ...etc), puis Hub-Link 2 (i865, i875) et le MuTIOL chez SiS, le 648 ayant innoguré la version "1G". Actuellement, sans parler des solutions HyperTransport AMD64, la seule technologie pouvant rivaliser en terme de bande passante est l'Ultra VLink de VIA, présent uniquement sur le non-encore disponilbe VIA PT880 et promettant 1 Go/s également

Passons aux caractéristiques du Southbridge :

- Southbridge SiS964

Passons maintenant au Southbridge qui accompagne le SiS655TX. Celui-ci, le SiS964, est l'évolution du SiS963 qu'on connaît maintenant depuis plus d'un an et qui équipait le SiS655. Les différences entre le SiS963 et le SiS964 sont minces. En premier lieu, et c'est relativement rare, SiS a décidé de retirer une fonctionnalité dans le SiS964 : Le contrôleur Firewire. Adieu donc IEEE1394a, qui n'avait pas trop d'intérêt face aux solutions externes, car nécessitant un PHY. Au menu des améliorations, un contrôleur SATA RAID intégré qu'on attendait depuis longtemps. Voyons ici un tableau récapitulatif des différents Southbridges SiS depuis le SiS961 :

| SiS MuTIOL® Media I/O Family - Comparison Chart | |||||||

| South Bridge | 961 | 961B | 962 | 962L | 963 | 963L | 964 |

| MuTIOL® | 533MB/s | 533MB/s | 533MB/s | 533MB/s | 1GB/s | 1GB/s | 1GB/s |

| AC 97 Interface | O | O | O | O | O | O | O |

| Fast Ethernet / Home Network | O | O | O | O | O | O | O |

| ATA 133 | N/A | O | O | O | O | O | O |

| USB 2.0 | N/A | N/A | O | O | O | O | O |

| USB port | 6 | 6 | 6 | 6 | 6 | 6 | 8 |

| IEEE 1394a | N/A | N/A | O | N/A | O | N/A | N/A |

| Serial ATA & RAID Function | N/A | N/A | N/A | N/A | N/A | N/A | O |

Voyons le diagramme (fournis par SiS) de ce Southbridge :

Ecnhaînons maintenant avec le détails des différents controleurs du Southbridge SiS964.

- La Liaison Inter-bridge MuTIOL : Comme nous l'avons vu plus haut, il s'agit du bus MuTIOL 1G offrant une bande passante de 1.066 Go/s maximum théorique. Son principal but est de décharger le bus PCI des communications entre Northbridge et Southbridge.

- Le Controleur PCI : Le controleur PCI qui équipé le SiS964 permet la gestion de 6 ports PCIs Bus Master à la norme 2.2. Meme si son efficacité globale (difference entre le max théorique et la pratique) n'est pas aussi bonne que sur les chipsets Intel, elle s'en rapproche toutefois de prés et reste incomparablement meilleur que sur les chipset VIA non patché. Toujours pas de PCI 2.3 dans le SiS964...

- Le Controleur IDE SATA : Il peut gérer 4 unités UltraATA 33/66/100/133 en mode BusMaster par le biais de 2 canaux. Ceci dit, la grande nouveauté reste le SATA150 qui est maintenant géré nativement sur deux canaux. Une gestion du RAID 0, 1 et JBOD est également au programme comme nous l'avons détaillé plus bas

- Le Controleur LAN : Comme tout les southbridge recents, le 964 supporte, via un PHY, l'Ethernet 10/100 Mbits. Ceci dit, il est quasi-systématiquement remplacé par un chip MAC+PHY externe sur les carte-mère un tant soit peu évoluée.

- Le Controleur LPC : le controleur LPC (Low Pin Count) permet de connecter le controleur Super I/O au Southbridge. Il controle donc indirectements, les ports PS2, LPT, les ports IR et le controleur de Disquette

- Le Controleur USB : Le SiS964 supporte la norme USB 1.1 ainsi que la norme USB 2.0. Il supporte donc 3 controleurs OHCI pour un maximum de 6 ports USB 1.1 et 1 controleur EHCI pour un maximum de 2 ports USB 2.0. Au total, 8 ports USB sont supportés, mais seulement 2 à la norme USB 2.0.

- Le Controleur AC97 : Il permet la gestion via une interface externe de la norme Audio Software AC'97 2.3 sur 6 cannaux

A noter que les cartes mères à base de SiS655TX/964 seront souvent équipées d'un nouveau venu dans la gamme de contrôleurs SiS, le SiS180. Il s'agit en fait d'un controleur SATA RAID fortement sponsorisé par Silicon Image. Voici les modes que vous risquez de rencontrer le plus souvent :

Pour rappel, Voici les différents modes de RAID et JBOD supportés par ces composants :

Bref un ensemble très convainquant sur le papier qui doit maintenant faire ses preuves dans la pratique. Après plus d'un an de travail sur le SiS655, SiS devrait nous proposer ici un chipset aboutis aux fonctionnalités et performances de premier ordre. C'est ce que nous verrons dans la partie pratique de ce test.