| Sommaire: |

Présentation type SiS648

Présentation du Chipset (SiS648)

Comme nous l'avons dit en introduction, le SiS648 est la troisieme génération de chipset SiS pour l'architecture Pentium 4 d'Intel. Il est le successeur du SiS645dx, lui meme successeur du SiS645 premier du nom. Commencons tout d'abord par observer, sous la forme d'un tableau, les principales differences qu'on peut trouver entre ces différentes générations :

| Chipset |

SiS

645 |

SiS

645dx |

SiS

648 |

| Lancement | Novembre

2001 |

Fevrier

2002 |

Juin

2002 |

| Plateforme | Socket

478 |

Socket

478 |

Socket

478 |

| Processeur Supportés | Intel

Pentium 4 |

Intel

Pentium 4 |

Intel

Pentium 4 |

| Northbridge | SiS

645 |

SiS

645dx |

SiS

648 |

| FSB officiel (officieux) | 100

MHz |

100/(133)

MHz |

100/133

MHz |

| Support de l'HyperThreading | non |

à partir de rev B0 |

à partir de rev B0 |

| Bus Mémoire officiel (officieux) | 100/133/166

MHz |

100/133/166

MHz |

100/133/166/(200)

MHz |

| Bus Asynchrone | oui |

oui |

oui |

| # de slots DIMM (> DDR333) | 3 |

3 |

4 |

| # de slots DIMM (=<DDR333) | 2 |

2 |

2 |

| Memory max | 3072

MB |

3072

MB |

3072

MB |

| Support SDRAM | oui |

oui |

non |

| Support DDR-SDRAM | oui |

oui |

oui |

| Norme AGP Supportée | 1x/2x/4x |

1x/2x/4x |

4x/8x |

| Version du bus AGP | 2.0 |

2.0 |

2.0/3.0 |

| Bus d'interconnexion | MuTIOL |

MuTIOL |

MuTIOL |

| Bande-passante | 533

Mo/s |

533

Mo/s |

1

Go/s |

| Southbridge | SiS

961 |

SiS

961B |

SiS

963 |

| Interconnexion | MuTIOL (533 Mo/s) |

MuTIOL (533 Mo/s) |

MuTIOL (1 Go/s) |

| Ultra-DMA/33/66/100 | oui/oui/oui |

oui/oui/oui |

oui/oui/oui |

| Ultra-DMA/133 | non |

oui |

oui |

| Ports USB Max. | 4 |

6 |

6 |

| Gestion de l'USB 2.0 | non |

non |

oui |

| Slots PCI Max. | 6 |

6 |

6 |

| Gestion du FireWire | non |

non |

oui |

| Ports FireWire Max. | n/a |

n/a |

6 |

| Controleur AC97 | oui |

oui |

oui |

| Gestion de l'ACPI | oui |

oui |

oui |

Ceci donne une vue globale de l'évolution qu'a connu le SiS645 pour arriver aujourd'hui au SiS648. Cette évolution a touché non seulement le Northbridge, qui gére l'interaction entre le CPU, la ram et l'AGP, mais aussi le Southbridge, qui controle tout les périphériques "lents" (PCI, IDE, USB, ...etc). Les evolutions sont importantes entre, par exemple, le Southbridge SiS 961 et le recent 963 qui accompagne le SiS 648. A noter que le SiS648 ne supporte la technologie HyperThreading d'Intel qu'a partie de la révision B0. Commencons notre étude par le Northbridge.

- NorthBridge SiS648

Comme nous l'avons vu précedemment, le SiS648 est la troisiéme évolution du SiS645. Il est aussi le successeur direct du SiS645dx, sorti il y a maintenant quelques mois. Au niveau du Northbridge, on peut vraiment parler de simple évolution plutot que de révolution. La principale nouvelle caractéristique est l'implémentation de l'AGP 8x.

L'AGP 8x (ou AGP v3.0) propose un débit de 2.1 Go/s là où l'AGP 4x est limité à 1 Go/s. Le signaux de données ont toujours une amplitude de 1.5 Volts, ce qui permet à l'AGP 8x d'accepter aussi les cartes AGP 4x. Par contre, il sera impossible d'utiliser une carte AGP 2x ou 1x à cause de la tension de 3.3 Volts qu'elles utilisent. Les spécifications de la version 3.0 de la norme AGP sont disponibles ici. Elles contiennent un tableau définissant les changement entre l'AGP 2.0 (4x) et l'AGP 3.0 (8x)

| Change |

Section |

Classification |

Core-Logic Impact |

Graphics Card Impact |

| 8X (533MT/s) transfer rate for Data and Side-band Address (SBA) | 2.1.2 |

Performance |

Required |

Required |

| Parallel terminated, low voltage signaling | 2.1 |

Performance |

Required |

Required |

| Hardware enforced coherency outside GART range for all transactions | 2.4.1 |

Feature Change |

Required |

Optional |

| "Long" Transaction Types Removed | 2.3.2 |

Feature Removal |

Required |

Required |

| No PIPE mode Addresses | 2.3.1 |

Feature Removal |

Need Not support

PIPE |

Required |

| High Priority Transaction Support Removed | 2.3.2 |

Feature Removal |

Required |

|

| Some changes to ordering rules | 2.3.4 |

Performance |

Optional |

Required |

| No Support for 3.3 V AGP signaling | 2.4.2 |

Feature Removal

1.5V AGP signaling still supported in "Universal Mode" |

Need not support

3.3V AGP |

Can't use 3.3V

AGP |

| Calibration Cycle | 2.1.3 |

Performance |

Required |

Required |

| Core-Logic AGP Resources in PCI-to-PCI Bridge | 2.5 |

Feature Enhancement |

Optional |

Not Required |

| Dynamic Bus Inversion | 2.1.3b |

Performance |

Required |

Required |

Outre cette particularité que pour le moment, peu de gens utiliserons (a part le Xabre, aucun GPU ne gére actuellement l'AGP 8x, le NV28 de nVidia devrait etre le prochain), l'innovation attendue pour le SiS648 était la gestion de la DDR400 (200 Mhz). Concernant le support de la DDR400, on s'attendait a un support officiel, comme nous l'avions vu au CeBit. Au dernier moment, SiS a décidé de ne pas valider son chipset en DDR400, du au manque de spécification. C'est une bonne chose ! Au contraire de VIA qui n'a pas hésiter a sortir son P4X400 avec le support officiel de la DDR400 et qui semble rencontre énormément de problemes, SiS a préféré la voie de la stabilité et des normes reconnues. Bon Choix. Surtout que, pour les intrépides, le support DDR400 est bien sur proposé dans le BIOS des cartes de maniéres non-officielles. Revoyons rapidement les comparaisons entre les différents types de mémoires comparés aux bus des pentium 4 :

Comme on le voit, la DDR 400 equivaut théoriquement à la Rambus PC800 et est parfaitement adaptée au bus 400 QDR des Pentiums 4 meme si il faudra attendre la DDR-II pour contenter les P4 sur bus 533 QDR. A noter que le SiS648 gére un maximum de 3 Go de DDR-SDRAM PC1600/2100 sur trois slots, mais comme beaucoup d'autres, seulement 2 Go sur 2 Slots pour de la mémoire PC2700 (DDR333)

Le dernier point interessant de distinction entre le SiS645dx et le SiS648 est le bus de communication inter-bridge baptisé MuTIOL. Ce bus, créé principalement dans le but de décharger le bus PCI des echanges Northbridge/Southbridge, évolue avec le couple 648/963. Voyons ca :

- MuTIOL (Multi-Threaded I/O Link) 1 Go/s

De la meme facon que le V-Link de Via ou le Hub-Link d'Intel, le bus MuTIOL a pour principal interet de laisse respirer le bus PCI lors des echanges entre les deux composants. Les SiS645 et 645dx communiquaient via un bus de données 16 bits Bi-Directionnel cadencé à 266 Mhz, ce qui lui permettait d'obtenir 533 Mo/s de bande passante. Pour le 648 et le 655, SiS à boosté son MuTIOL en proposant un bus cadencé à 533 Mhz, ce qui permet une bande passante maximale théorique de 1.066 Go/s. Vu l'intégration de l'USB 2.0 et du FireWire, grands consommateurs de ressources, on ne peut que saluer cette initiative. Voici un petit comparatif des performances qu'offre les differents bus de communications Northbridge/Southbridge.

On retrouve le V-Link dans les premiers chipsets VIA (P4X266, P4X266A, ...etc), le V-Link 2 dans les chipset plus recents (P4X400, ...etc), le Hub-Link chez Intel (i845PE, i845GE, i850E, ...etc) et le MuTIOL chez SiS, le 648 innogurant la version "1G".

Passons aux caractéristiques du Southbridge :

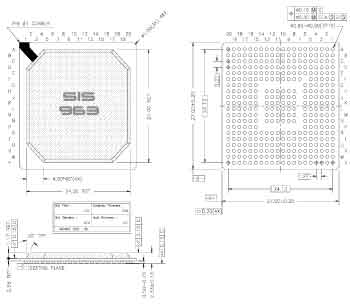

- SouthBridge SiS963

Le Southbridge 963 compléte donc le SiS648. Il gére bien entendu le nouveau bus MuTIOL 1G dont nous avons parlé plus haut, mais apporte lui aussi sont lot de nouveautés. Au programmé, on trouvera principalement le support de l'USB 2.0 et du Firewire. Pour info, une version MuTIOL 533 du SiS963 existe, il s'agit du SiS962 qu'on retrouvera trés probablement sur des cartes d'entrée de gamme, voir avec des Northbridges 645/645dx.

Voyons le diagramme (fournis par SiS) de ce Southbridge :

Passons maintenant au détails des différents controleurs du Southbridge SiS963.

- La Liaison inter-bridge : Comme nous l'avons vu plus haut, il s'agit du bus MuTIOL 1G offrant une bande passante de 1.066 Go/s maximum théorique

- Le Controleur PCI : Le controleur PCI qui équipé le SiS963 permet la gestion de 6 ports PCIs Bus Master à la norme 2.2. Meme si son efficacité globale (difference entre le max théorique et la pratique) n'est pas aussi bonne que sur les chipsets Intel, elle s'en rapproche toutefois de prés et reste incomparablement meilleur que sur les chipset VIA non patché.

- Le Controleur IDE : Il peut gérer 4 unités UltraATA 33/66/100/133 en mode BusMaster par le biais de 2 canaux. L'arrivée de l'ATA133 permettra la gestion des disques durs de plus de 137 Go sans problemes.

- Le Controleur LAN : Comme tout les southbridge recents, le 963 supporte, via un PHY, l'Ethernet 10/100 Mbits. Dans le cas de SiS, nous savons de source sûre que le prochain Southbridge, le SiS 963B supportera aussi un controleur pour modem ADSL interne au chipset.

- Le Controleur LPC : le controleur LPC (Low Pin Count) permet de connecter le controleur Super I/O au Southbridge. Il controle donc indirectements, les ports PS2, LPT, les ports IR et le controleur de Disquette

- Le Controleur USB : Le SiS963 supporte la norme USB 1.1 ainsi que la norme USB 2.0. Il support donc 3 controleurs OHCI pour un maximum de 6 ports USB 1.1 et 1 controleur EHCI pour un maximum de 2 ports USB 2.0.

- Le Controleur Firewire IEEE1394A : Autre nouveauté, le support d'un controleur Firewire 1394a OHCI 1.1. Pour fonctionner il necessite la précense d'un PHY qui gérera trois canaux firewire avec des taux de transferts de 100/200/400 Mb/s.

- Le Controleur AC97 : Il permet la gestion via une interface externe de la norme Audio Software AC'97 sur 6 cannaux

Bref, le couple 648/963 supporte toute les normes récentes et rien

de semble manquer a l'appel.