| Sommaire: |

IDF Fall 2004 : Process 65 nm

C'est dit : Après le 90 nm accouché par Intel avec 6 mois de retard, c'est le 65 nm qui fera son apparition. Première nouvelle, celui-ci sera "On Time" pour l'année prochaine et ne devrait pas subir de retard. La raison ? Les fabs P1262 (nom de code du process 90 nm) sont également prêtes dès maintenant pour le process P1264 (65 nm) et ne nécessitent pas d'adaptations majeures comme ça avait été le cas pour le passage de 130 nm vers 90 nm. Intel est d'ailleurs dès maintenant capable de produire des chips SRAM de 70 Mbits sur des wafers de 300mm en 65 nm. Pour en savoir plus, nous avons fait une table ronde avec Monsieur (notez le 'M' majuscule) Mark Bohr, grand manitou des process de fabrications chez Intel.

Bref, M. Bohr semble donc avoir trouvé la bonne combinaison pour produire du 65 nm en temps et en heure. Concernant le 90 nm, la production depassera ce semestre la production des CPUs en 130 nm et la majorité des processeurs produits seront donc en 90nm. Au sujet du futur 65 nm, voyons maintenant l'évolution attendue des procédés de gravures :

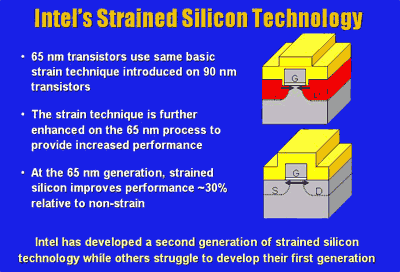

La prochaine étape sera donc le 45 nm, puis le 32 nm. Intel ne se gêne d'ailleurs pas pour bien indiquer que le 65 nm est déjà quasiment terminé alors que "certains" (qui ont des toiles d'araignées sur leur portail) ont encore des problèmes de Yield avec leurs 90 nm. La porte ou "gate" d'un transistor ne fait maintenant plus que 35 nm, soit la moitié de celle utilisées dans les CPUs Northwood. L'alliage utilisé est maintenant du nickel-silicide. Autre grosse nouveauté du process 90 nm, l'amélioration du fameux Strained Silicon. En effet, le process de création a été grandement amélioré :

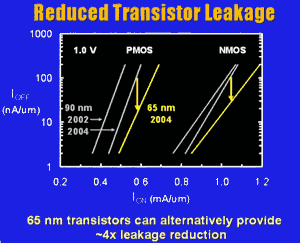

Traduisez de nouveau"others" par "other with spider web on their portal". Cette nouvelle génération de Strained Silicon devrait permettre de régler une bonne partie des problèmes de leakage rencontré avec le 90 nm. En effet, Intel annonce une réduction du leakage pouvant aller jusqu'à 4x et une augmentation de 30% de la performance du transistor, ce qui est loin d'être négligeable :

|

|

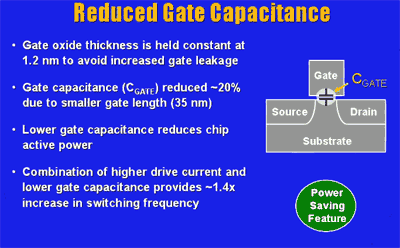

Autre avantage, la réduction de la capacitance (effet condensateur) de la porte du transistor qui peut atteindre 20 % :

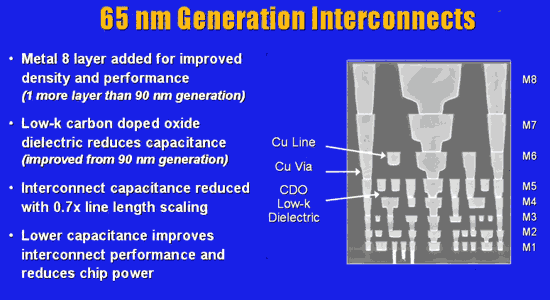

Cette amélioration permettra d'augmenter la fréquence maximale du transistor de 40%, ce qui est également intéressant. Un mot également sur le procédé de photolithogravure qui continue à utiliser le longueur d'onde de 193 nm, initiée avec le 90 nm et qui se terminera avec le 45 nm. Au delà, il faudra passer en procédé EUV où la taille de l'onde passera à 13 nm. Le 65 nm ajoutera encore une couche d'interconnexion dont le nombre total passera de 7 à 8 :

Le passage aux 65 nm étant un simple shrink pour le Prescott, on peut donc s'attendre à une forte baisse de la consommation électrique puisqu'aucun transistor ne sera rajouté et que le process est clairement optimisé pour l'économie d'énergie. Les futurs CPU Bi-Core en 65 nm ne consommeront donc pas beaucoup plus que les actuels 90 nm. Pour accentuer encore cet état de fait, Intel a ajouté un procédé de désactivation des blocs de caches permettant de mettre en sommeil les transistors non utilisés. Cette technologie existe déjà sur le Pentium M pour des quadrants de mémoires, mais sera grandement améliorée avec le 65 nm :

Le principe permettra donc une économie d'energie encore plus importante dans le Yonah, qui sera un Dothan Bi-Core. Ceci dit, cette amélioration sera également la bienvenue dans les Desktop où la dissipation thermique commence sérieusement à devenir critique à tout point de vue. Au final, la technologie 65 nm permettra de loger dix millions de transistors dans une zone de 1 mm², équivalente à une bille de stylo :

Espérons maintenant que ce process sera bien en production dès la seconde moitié de 2005, comme attendu...